# PLDC20RA10

# Reprogrammable Asynchronous CMOS Logic Device

- Features

- Advanced-user programmable macrocell

- CMOS EPROM technology for reprogrammability

- Up to 20 input terms

- 10 programmable I/O macrocells

- Output macrocell programmable as combinatorial or asynchronous D-type registered output

- Product-term control of register clock, reset and set and output enable

- Register preload and power-up reset

- Four data product terms per output macrocell

- Fast

- Commercial

- t<sub>PD</sub> = 15 ns

- $t_{CO} = 15 \text{ ns}$

- t<sub>SU</sub> = 7 ns

- Military

- t<sub>PD</sub> = 20 ns

- t<sub>CO</sub> = 20 ns t<sub>SU</sub> = 10 ns

- Low power

- I<sub>CC</sub> max 80 mA (Commercial)

### -I<sub>CC</sub> max = 85 mA (Military)

- · High reliability

- -Proven EPROM technology

- ->2001V input protection

- -100% programming and functional testing

- Windowed DIP, windowed LCC, DIP, LCC, PLCC available

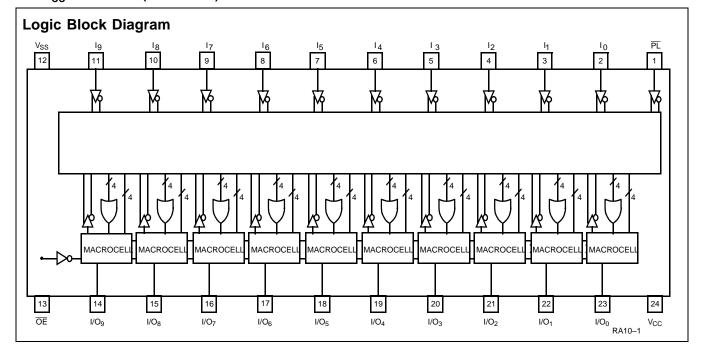

#### **Functional Description**

The Cypress PLDC20RA10 is a high-performance, second-generation programmable logic device employing a flexible macrocell structure that allows any individual output to be configured independently as a combinatorial output or as a fully asynchronous D-type registered output.

The Cypress PLDC20RA10 provides lower-power operation with superior speed performance than functionally equivalent bipolar devices through the use of high-performance 0.8-micron CMOS manufacturing technology.

The PLDC20RA10 is packaged in a 24 pin 300-mil molded DIP, a 300-mil windowed cerDIP, and a 28-lead square lead-less chip carrier, providing up to 20 inputs and 10 outputs. When the windowed device is exposed to UV light, the 20RA10 is erased and can then be reprogrammed.

3901 North First Street

San Jose

CA 95134

408-943-2600

Revised March 26, 1997

### **Selection Guide**

| Generic Part | t <sub>P</sub> | <sub>D</sub> ns | t <sub>S</sub> | t <sub>SU</sub> ns |       | t <sub>CO</sub> ns |       | ; ns |

|--------------|----------------|-----------------|----------------|--------------------|-------|--------------------|-------|------|

| Number       | Comʻl          | Mil             | Com'l          | Mil                | Com'l | Mil                | Com'l | Mil  |

| 20RA10-15    | 15             |                 | 7              |                    | 15    |                    | 80    |      |

| 20RA10-20    | 20             | 20              | 10             | 10                 | 20    | 20                 | 80    | 85   |

| 20RA10-25    |                | 25              |                | 15                 |       | 25                 |       | 85   |

| 20RA10-35    |                | 35              |                | 20                 |       | 35                 |       | 85   |

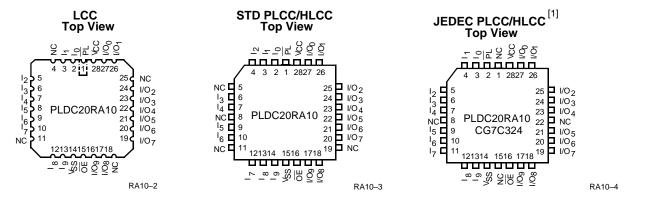

#### **Pin Configurations**

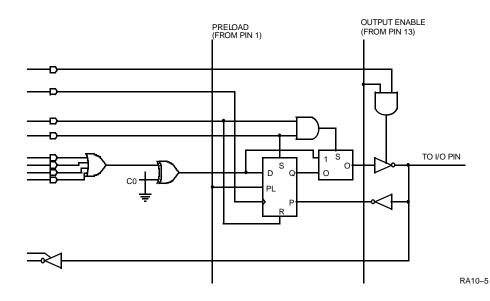

#### **Macrocell Architecture**

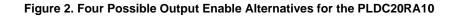

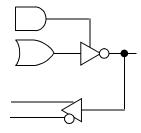

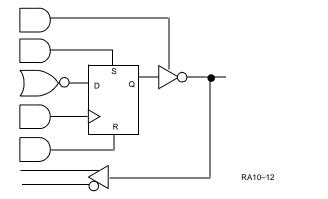

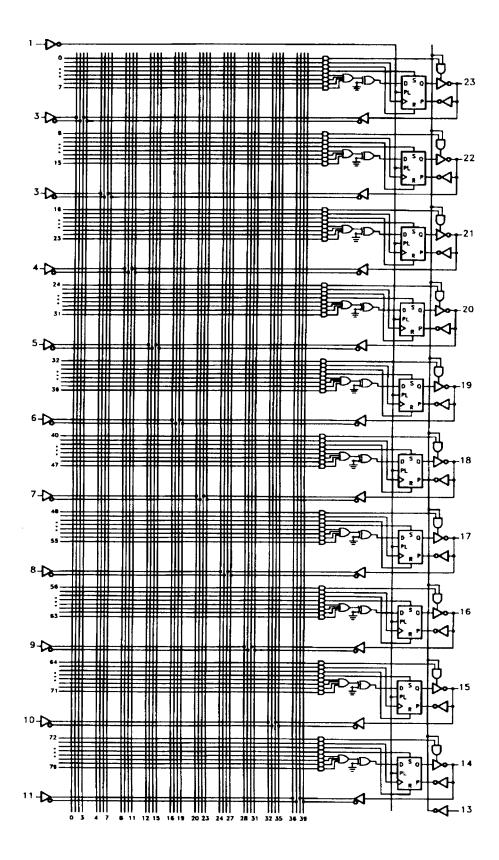

*Figure 1* illustrates the architecture of the 20RA10 macrocell. The cell dedicates three product terms for fully asynchronous control of the register set, reset, and clock functions, as well as, one term for control of the output enable function.

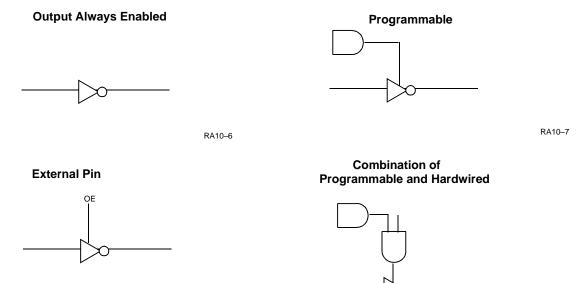

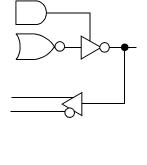

The output enable product term output is ANDed with the input from pin 13 to allow either product term or hardwired external control of the output or a combination of control from both sources. If product-term-only control is selected, it is automatically chosen for all outputs since, for this case, the external output enable pin must be tied LOW. The active polarity of each output may be programmed independently for each output cell and is subsequently fixed. *Figure 2* illustrates the output enable options available.

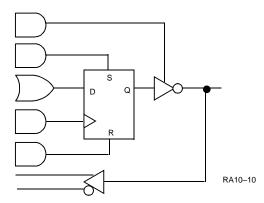

When an I/O cell is configured as an output, combinatorial-only capability may be selected by forcing the set and reset product term outputs to be HIGH under all input conditions. This is achieved by programming all input term programming cells for these two product terms. *Figure 3* illustrates the available output configuration options.

An additional four uncommitted product terms are provided in each output macrocell as resources for creation of user-defined logic functions.

### Programmable I/O

Because any of the ten I/O pins may be selected as an input, the device input configuration programmed by the user may vary from a total of nine programmable plus ten dedicated inputs (a total of nineteen inputs) and one output down to a ten-input, ten-output configuration with all ten programmable I/O cells configured as outputs. Each input pin available in a given configuration is available as an input to the four control product terms and four uncommitted product terms of each programmable I/O macrocell that has been configured as an output.

An I/O cell is programmed as an input by tying the output enable pin (pin 13) HIGH or by programming the output enable product term to provide a LOW, thereby disabling the output buffer, for all possible input combinations.

When utilizing the I/O macrocell as an output, the input path functions as a feedback path allowing the output signal to be fed back as an input to the product term array. When the output cell is configured as a registered output, this feedback path may be used to feed back the current output state to the device inputs to provide current state control of the next output state as required for state machine implementation.

#### **Preload and Power-Up Reset**

Functional testability of programmed devices is enhanced by inclusion of register preload capability, which allows the state of each register to be set by loading each register from an external source prior to exercising the device. Testing of complex state machine designs is simplified by the ability to load an arbitrary state without cycling through long test vector sequences to reach the desired state. Recovery from illegal states can be verified by loading illegal states and observing recovery. Preload of a particular register is accomplished by impressing the desired state on the register output pin and lowering the signal level on the preload control pin (pin1) to a logic LOW level. If the specified preload set-up, hold and pulse width minimums have been observed, the desired state is loaded into the register. To insure predictable system initialization, all registers are preset to a logic LOW state upon power-up, thereby setting the active LOW outputs to a logic HIGH.

Note:

<sup>.</sup> The CG7C324 is the PLDC20RA10 packaged in the JEDEC-compatible 28-pin PLCC pinout. Pin function and pin order is identical for both PLCC pinouts. The principal difference is in the location of the "no connect" (NC) pins

RA10-8

RA10-9

#### Registered/ActiveLOW

#### **Combinatorial/Active LOW**

RA10-11

### Registered/Active HIGH

#### **Combinatorial/Active HIGH**

RA10-13

#### Figure 3. Four Possible Macrocell Configurations for the PLDC20RA10

\_\_\_\_\_

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guide-lines, not tested.)

| Storage Temperature                                   | –65°C to +150°C   |

|-------------------------------------------------------|-------------------|

| Ambient Temperature with<br>Power Applied             | –55°C to +125°C   |

| Supply Voltage to Ground Potential (Pin 24 to Pin 12) | 0.5V to +7.0V     |

| DC Voltage Applied to Outputs<br>in High Z State      | –0.5V to +7.0V    |

| DC Input Voltage                                      | –3.0 V to + 7.0 V |

| Output Current into Outputs (LOW)                     | 16 mA             |

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015) | >2001V  |

|------------------------------------------------------------|---------|

| Latch-Up Current                                           | >200 mA |

| DC Program Voltage                                         | 13.0V   |

#### **Operating Range**

| Range                   | Ambient<br>Temperature | v <sub>cc</sub> |

|-------------------------|------------------------|-----------------|

| Commercial              | 0°C to +75°C           | 5V ± 10%        |

| Military <sup>[2]</sup> | –55°C to +125°C        | 5V ± 10%        |

#### Electrical Characteristics Over the Operating Range<sup>[3]</sup>

| Parameter        | Description                                 | Test                                                                     | Conditions                                                          |     | Min. | Max. | Unit |

|------------------|---------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------|-----|------|------|------|

| V <sub>OH</sub>  | Output HIGH Voltage                         | V <sub>CC</sub> = Min.,                                                  | Com'l                                                               | 2.4 |      | V    |      |

|                  |                                             | V <sub>IN</sub> =V <sub>IH</sub> or V <sub>IL</sub>                      | I <sub>OH</sub> = -2 mA                                             | Mil |      |      |      |

| V <sub>OL</sub>  | Output LOW Voltage                          | $V_{CC} = Min.,$ $I_{OL} = 8 mA$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$ |                                                                     |     |      | 0.5  | V    |

| V <sub>IH</sub>  | Input HIGH Level                            | Guaranteed Input Logica                                                  | Guaranteed Input Logical HIGH Voltage for All Inputs <sup>[4]</sup> |     |      |      | V    |

| V <sub>IL</sub>  | Input LOW Level                             | Guaranteed Input Logical LOW Voltage for All Inputs <sup>[4]</sup>       |                                                                     |     |      | 0.8  | V    |

| I <sub>IX</sub>  | Input Leakage Current                       | $V_{SS} \le V_{IN} \le V_{CC}, V_{CC} = Max$                             |                                                                     |     |      | +10  | μΑ   |

| I <sub>OZ</sub>  | Output Leakage Current                      | $V_{CC}$ = Max., $V_{SS} \le V_{OUT} \le V_{CC}$                         |                                                                     |     |      | +40  | μΑ   |

| I <sub>SC</sub>  | Output Short Circuit Current <sup>[5]</sup> | $V_{CC}$ = Max., $V_{OUT}$ = 0.5                                         | V <sub>CC</sub> = Max., V <sub>OUT</sub> = 0.5V <sup>[6]</sup>      |     |      |      | mA   |

| I <sub>CC1</sub> | Standby Power Supply Current                | V <sub>CC</sub> = Max., V <sub>IN</sub> = GND Outputs Open Com'l         |                                                                     |     |      | 75   | mA   |

|                  |                                             |                                                                          |                                                                     | Mil |      | 80   | mA   |

| I <sub>CC2</sub> |                                             |                                                                          | x., Outputs Disabled (In High Z Cor                                 |     |      | 80   | mA   |

|                  | Frequency <sup>[5]</sup>                    | State) Device Operating at f <sub>MAX</sub>                              |                                                                     | Mil |      | 85   | mA   |

#### Capacitance<sup>[5]</sup>

| Parameter        | Description        | Test Conditions                      | Max. | Unit |

|------------------|--------------------|--------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 2.0 V @ f = 1 MHz  | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 2.0 V @ f = 1 MHz | 10   | pF   |

Notes:

2. T<sub>A</sub> is the "instant on" case temperature.

3. 4.

The state of this specification for Gase temperature. See the last page of this specification for Group A subgroup testing information. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included. Tested initially and after any design or process changes that may affect these parameters. Not more than one output should be tested at a time. Duration of the short circuit should not be more than one second. V<sub>OUT</sub> = 0.5 V has been chosen to 5. 6. avoid test problems caused by tester ground degradation.

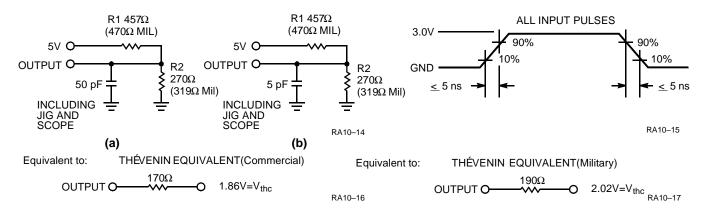

## AC Test Loads and Waveforms (Commercial)

| Parameter           | V <sub>th</sub>  | Output Waveform Measurement Level           |

|---------------------|------------------|---------------------------------------------|

| t <sub>PXZ(-)</sub> | 1.5V             | V <sub>OH</sub> 0.5V V <sub>X</sub> RA10-18 |

| t <sub>PXZ(+)</sub> | 2.6V             | V <sub>OL</sub> 0.5V V <sub>X</sub>         |

| t <sub>PZX(+)</sub> | V <sub>thc</sub> | V <sub>X</sub> 0.5V V <sub>OH</sub>         |

| t <sub>PZX(-)</sub> | V <sub>thc</sub> | V <sub>X</sub> 0.5V V <sub>OL</sub> RA10-21 |

| t <sub>ER(-)</sub>  | 1.5V             | V <sub>OH</sub> 0.5V V <sub>X</sub> RA10-22 |

| t <sub>ER(+)</sub>  | 2.6V             | V <sub>OL</sub> 0.5V V <sub>X</sub>         |

| t <sub>EA(+)</sub>  | V <sub>thc</sub> | V <sub>X</sub> 0.5V. ↓ V <sub>OH</sub>      |

| t <sub>EA(-)</sub>  | V <sub>thc</sub> | V <sub>X</sub> 0.5V V <sub>OL</sub> RA10-25 |

(c)

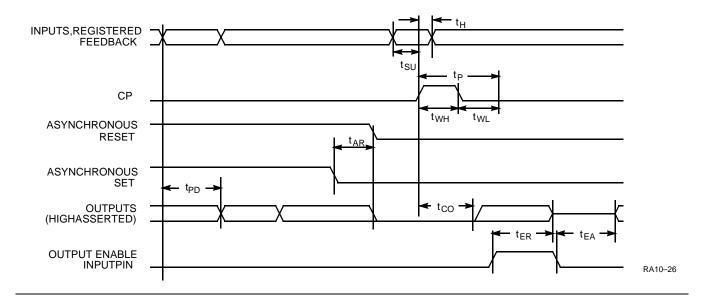

## Switching Characteristics Over the Operating Range<sup>[3, 7, 8]</sup>

|                  |                                                        | Commercial |      |      |      | Military |      |      |      |      |      |      |

|------------------|--------------------------------------------------------|------------|------|------|------|----------|------|------|------|------|------|------|

|                  |                                                        | Ì          | 15   | -    | 20   |          | 20   | -25  |      | -35  |      | 1    |

| Parameter        | Description                                            | Min.       | Max. | Min. | Max. | Min.     | Max. | Min. | Max. | Min. | Max. | Unit |

| t <sub>PD</sub>  | Input or Feedback to<br>Non-Registered Output          |            | 15   |      | 20   |          | 20   |      | 25   |      | 35   | ns   |

| t <sub>EA</sub>  | Input to Output Enable                                 |            | 15   |      | 20   |          | 20   |      | 30   |      | 35   | ns   |

| t <sub>ER</sub>  | Input to Output<br>Disable                             |            | 15   |      | 20   |          | 20   |      | 30   |      | 35   | ns   |

| t <sub>PZX</sub> | Pin 13 to Output<br>Enable                             |            | 12   |      | 15   |          | 15   |      | 20   |      | 25   | ns   |

| t <sub>PXZ</sub> | Pin 13 to Output<br>Disable                            |            | 12   |      | 15   |          | 15   |      | 20   |      | 25   | ns   |

| t <sub>CO</sub>  | Clock to Output                                        |            | 15   |      | 20   |          | 20   |      | 25   |      | 35   | ns   |

| t <sub>SU</sub>  | Input or Feedback<br>Set-Up Time                       | 7          |      | 10   |      | 10       |      | 15   |      | 20   |      | ns   |

| t <sub>H</sub>   | Hold Time                                              | 3          |      | 5    |      | 3        |      | 5    |      | 5    |      | ns   |

| t <sub>P</sub>   | Clock Period<br>(t <sub>SU</sub> + t <sub>CO)</sub>    | 22         |      | 30   |      | 30       |      | 40   |      | 55   |      | ns   |

| t <sub>WH</sub>  | Clock Width HIGH <sup>[5]</sup>                        | 10         |      | 13   |      | 12       |      | 18   |      | 25   |      | ns   |

| t <sub>WL</sub>  | Clock Width LOW <sup>[5]</sup>                         | 10         |      | 13   |      | 12       |      | 18   |      | 25   |      | ns   |

| f <sub>MAX</sub> | Maximum Frequency (1/t <sub>P</sub> ) <sup>[5]</sup>   | 45.5       |      | 33.3 |      | 33.3     |      | 25.0 |      | 18.1 |      | MHz  |

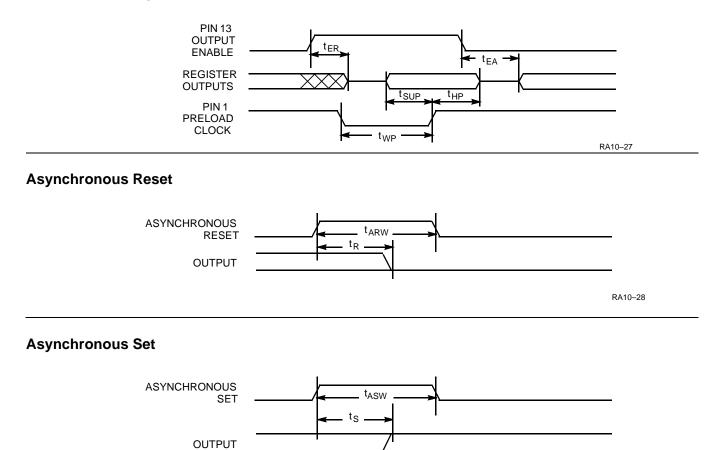

| t <sub>S</sub>   | Input of Asynchronous<br>Set to Registered Output      |            | 15   |      | 20   |          | 20   |      | 25   |      | 40   | ns   |

| t <sub>R</sub>   | Input of Asynchronous<br>Reset to Registered<br>Output |            | 15   |      | 20   |          | 20   |      | 25   |      | 40   | ns   |

| t <sub>ARW</sub> | Asynchronous Reset<br>Width <sup>[5]</sup>             | 15         |      | 20   |      | 20       |      | 25   |      | 25   |      | ns   |

| t <sub>ASW</sub> | Asynchronous S-Width <sup>[5]</sup>                    | 15         |      | 20   |      | 20       |      | 25   |      | 25   |      | ns   |

| t <sub>AR</sub>  | Asynchronous Set/<br>Reset Recovery Time               | 10         |      | 12   |      | 12       |      | 15   |      | 20   |      | ns   |

| t <sub>WP</sub>  | Preload Pulse Width                                    | 15         |      | 15   |      | 15       |      | 15   |      | 15   |      | ns   |

| t <sub>SUP</sub> | Preload Set-Up Time                                    | 15         |      | 15   |      | 15       |      | 15   |      | 15   |      | ns   |

| t <sub>HP</sub>  | Preload Hold Time                                      | 15         |      | 15   |      | 15       |      | 15   |      | 15   |      | ns   |

Notes:

Part (a) of AC Test Loads was used for all parameters except t<sub>EA</sub>, t<sub>ER</sub>, t<sub>PZX</sub> and t<sub>PXZ</sub>, which use part (b).

The parameters t<sub>ER</sub> and t<sub>PXZ</sub> are measured as the delay from the input disable logic threshold transition to V<sub>OH</sub> - 0.5 V for an enabled HIGH output or V<sub>OL</sub> +0.5V for an enabled LOW output. Please see part (c) of AC Test Loads and Waveforms for waveforms and measurement reference levels.

## Switching Waveform

## Preload Switching Waveform

RA10-29

## PLDC20RA10

## **Functional Logic Diagram**

## **Ordering Information**

| I <sub>CC2</sub> | t <sub>PD</sub><br>(ns) | t <sub>SU</sub><br>(ns) | t <sub>CO</sub><br>(ns) | Ordering Code    | Package<br>Name | Package Type                        | Operating<br>Range |

|------------------|-------------------------|-------------------------|-------------------------|------------------|-----------------|-------------------------------------|--------------------|

| 80               | 15                      | 7                       | 15                      | PLDC20RA10-15JC  | J64             | 28-Lead Plastic Leaded Chip Carrier | Commercial         |

|                  |                         |                         |                         | PLDC20RA10-15PC  | P13             | 24-Lead (300-Mil) Molded DIP        |                    |

|                  |                         |                         |                         | CG7C324-A15JC    | J64             | 28-Lead Plastic Leaded Chip Carrier |                    |

|                  | 20                      | 10                      | 20                      | PLDC20RA10-20PC  | P13             | 24-Lead (300-Mil) Molded DIP        |                    |

|                  |                         |                         |                         | CG7C324-A20JC    | J64             | 28-Lead Plastic Leaded Chip Carrier |                    |

| 85               | 20                      | 10                      | 20                      | PLDC20RA10-20DMB | D14             | 24-Lead (300-Mil) CerDIP            | Military           |

|                  |                         |                         |                         | PLDC20RA10-20WMB | W14             | 24-Lead (300-Mil) Windowed CerDIP   |                    |

|                  | 25                      | 15                      | 25                      | PLDC20RA10-25DMB | D14             | 24-Lead (300-Mil) CerDIP            |                    |

|                  |                         |                         |                         | PLDC20RA10-25WMB | W14             | 24-Lead (300-Mil) Windowed CerDIP   |                    |

|                  | 35                      | 20                      | 35                      | PLDC20RA10-35DMB | D14             | 24-Lead (300-Mil) CerDIP            | 1                  |

|                  |                         |                         |                         | PLDC20RA10-35WMB | W14             | 24-Lead (300-Mil) Windowed CerDIP   | ]                  |

#### MILITARY SPECIFICATIONS Group A Subgroup Testing

### **DC Characteristics**

| Parameter       | Subgroups |

|-----------------|-----------|

| V <sub>OH</sub> | 1, 2, 3   |

| V <sub>OL</sub> | 1, 2, 3   |

| V <sub>IH</sub> | 1, 2, 3   |

| V <sub>IL</sub> | 1, 2, 3   |

| I <sub>IX</sub> | 1, 2, 3   |

| I <sub>OZ</sub> | 1, 2, 3   |

## **DC Characteristics**

| Parameter       | Subgroups |

|-----------------|-----------|

| I <sub>CC</sub> | 1, 2, 3   |

## **Switching Characteristics**

| Parameter        | Subgroups |

|------------------|-----------|

| t <sub>PD</sub>  | 9, 10, 11 |

| t <sub>PZX</sub> | 9, 10, 11 |

| t <sub>CO</sub>  | 9, 10, 11 |

| t <sub>SU</sub>  | 9, 10, 11 |

| t <sub>H</sub>   | 9, 10, 11 |

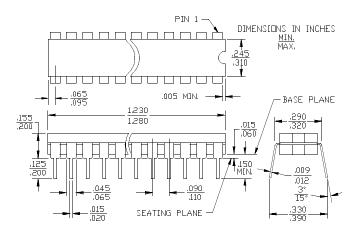

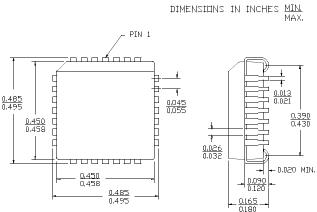

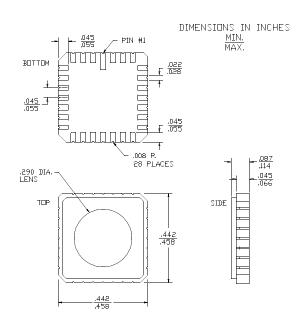

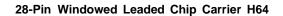

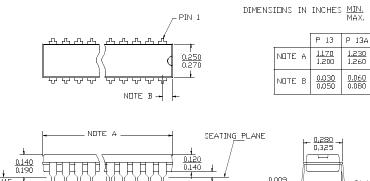

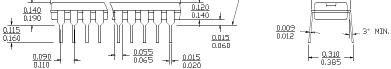

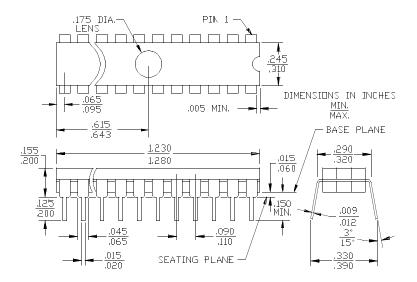

#### **Package Diagrams**

**24-Lead (300-Mil) CerDIP D14** MIL-STD-1835 D- 9Config.A

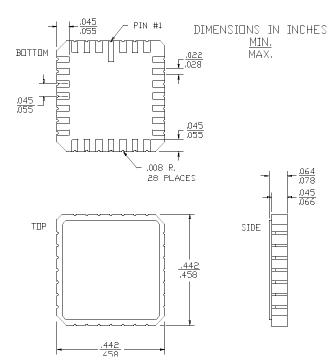

#### 28-Square L64 Carrier Chip Leadless MIL-STD-1835 C-4

28-Lead Plastic Leaded Chip Carrier J64

#### 28-Pin Windowed Leadless Chip Carrier Q64 MIL-STD-1835 C-4

## Package Diagrams (continued)

#### Package Diagrams (continued)

#### 24-Lead (300-Mil) Molded DIP P13/P13A

#### 24-Lead (300-Mil) Windowed CerDIP W14 MIL-STD-1835 D-9 Config.A

© Cypress Semiconductor Corporation, 1997. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor against all charges.

| Document Title: PLDC20RA10 Reprogrammable Asynchronous CMOS Logic Device<br>Document Number: 38-03012 |         |            |                 |                                               |

|-------------------------------------------------------------------------------------------------------|---------|------------|-----------------|-----------------------------------------------|

| REV.                                                                                                  | ECN NO. | Issue Date | Orig. of Change | Description of Change                         |

| **                                                                                                    | 106294  | 04/24/01   | SZV             | Change from Spec number: 38-00073 to 38-03012 |

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.